How to use Si4463 Wireless module to send and receive extra long packets

May . 2021

The Si4463 wireless module of SiliconLabs EZRadioPro series, TX FIFO and RX FIFO are only 64 bytes. So how torealize the sending and receiving of data packets exceeding 64 bytes? Need totediously split long packets into smaller packets of less than or equal to 64bytes, sending each packet separately, and then the receiver end splices thesepacket data back to the original long packet data? The answer is: no! Becausethe sending and receiving of long packets is implemented in the Si446xtransceiver chip is very simple.

Open the WDS software or check the API register description file.There are two interrupts that are very useful, namely TX_FIFO_ALMOST_EMPTY_PENDand RX_FIFO_ALMOST_FULL_PEND. These two interrupts mean that the TX FIFO datais about to be sent out or the RX FIFO is about to be filled. Then we only needto send and receive ultra-long packets based on these two interrupts.

For example,when the TX_FIFO_ALMOST_EMPTY_PEND interrupt is generated, the data isimmediately filled into the TX FIFO. The newly filled data will be sentimmediately following the previous data until the data packet is completelytransmitted. Finally, a transmission completion interrupt is generated,indicating that the packet data has been sent . It is also similar whenreceiving. When the received data is continuously filled in the RX FIFO, whenit is about to be filled, an RX_FIFO_ALMOST_FULL_PEND interrupt will begenerated. At this time, the RX FIFO will be read out immediately, and theempty FIFO can continue receiving new Data until the total received data isequal to the entire complete packet length, a receive completion interrupt isgenerated. The entire process is continuous. Depending on the packet length andthe set threshold, multiple TX_FIFO_ALMOST_EMPTY_PEND andRX_FIFO_ALMOST_FULL_PEND interrupts will be generated, but there will only beone interrupt for each packet data transmission completion and receptioncompletion, which is the same as the transmission and reception of shortpackets.

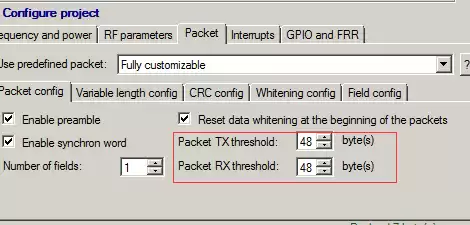

The setting interface of WDS is as follows:

Set configuration TX_FIFO_ALMOST_EMPTY and RX_FIFO_ALMOST_FULL thresholds

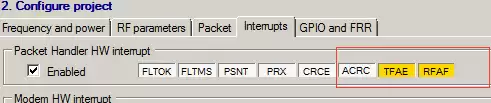

Enable thecorresponding interrupt

The user needs to add the corresponding reaction of the system whenTX_FIFO_ALMOST_EMPTY and RX_FIFO_ALMOST_FULL are detected in the code.

The above is some summary of sending long data packets in 4463, I hope it can be helpful to you.

+86-755-23080616

+86-755-23080616

sales@nicerf.com

sales@nicerf.com

Website: https://www.nicerf.com/

Address: 309-315, 3/F, Bldg A, Hongdu business building, Zone 43, Baoan Dist, Shenzhen, China

English

English